74HC4049, CMOS 4049

Betriebsspannung

Der 74HC4049 darf nur mit 3 V bis 6 V betrieben werden.

Der CMOS 4049 darf mit 3 V bis 15 V betrieben werden.

Die Eingänge des 74HC4049 und des CMOS 4049 dürfen mit bis zu +15 V betrieben werden.

Der 74HC4049 bzw. CMOS 4049 enthält sechs Inverter bzw. NOT-Gatter und ist ein Pegelwandler und Treiber (Buffer).

- Allgemeine Daten sind unter Familien digitaler Bauelemente beschrieben.

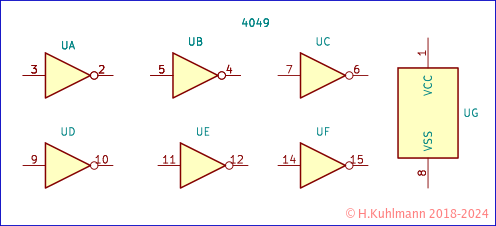

Symbol und Anschlussbelegung

- Der 74HC4049N bzw. CMOS 4049 hat ein 16-poliges Dual-In-Line-Gehäuse, DIL-Gehäuse.

Achtung: Die positive Betriebsspannung VDD liegt an Pin 1.

74HC4049

Der 74HC4049 ist in HCMOS-Technologie gefertigt und darf mit 3 V bis 6 V betrieben werden.

Der 74HC4049 kann am Eingang mit höheren Spannungen betrieben werden. Es sind bis +15 V am Eingang erlaubt.

CMOS 4049

Der CMOS 4049 ist in CMOS-Technologie gefertigt und für Versorgungsspannungen von 3 V bis 15 V geeignet.

Der CMOS 4049 kann am Eingang mit höheren Spannungen betrieben werden. Es sind bis +15 V am Eingang erlaubt.

Wahrheitstabelle

Beispiel Inverter (NOT-Gatter) UA

| Eingang | Ausgang |

| Pin 3 | Pin 2 |

| 0 | 1 |

| 1 | 0 |

Verwendung als Pegelwandler

Der 74HC4049 bzw. CMOS 4049 kann als Pegelwandler verwendet werden.

- Die Spannung am Eingang darf höher sein als die Versorgungsspannung.

- Beim 74HC4049 bzw. CMOS 4049 sind bis +15 V am Eingang erlaubt.

- Der LOW-Pegel der Eingangsspannung muss dem LOW-Pegel der derzeitigen Versorgungsspannung an Pin 1 entsprechen.

Belastbarkeit der Ausgänge

- Um den Logikpegel zu gewährleisten, darf ein Ausgang bei 5 V mit maximal 3,5 mA belastet werden.

- Wenn der 74HC4049 als Treiber verwendet wird,

- können 25 mA vom Ausgang geliefert oder gezogen werden.

- Der maximale Strom aller Ausgänge darf 50 mA nicht überschreiten.

- Wenn der CMOS 4049 als Treiber (Buffer) verwendet wird,

- können bei LOW etwa 10 mA in den Ausgang fließen

- und bei HIGH etwa 20 mA vom Ausgang geliefert werden.

- Der maximale Strom aller Ausgänge darf 50 mA nicht überschreiten.

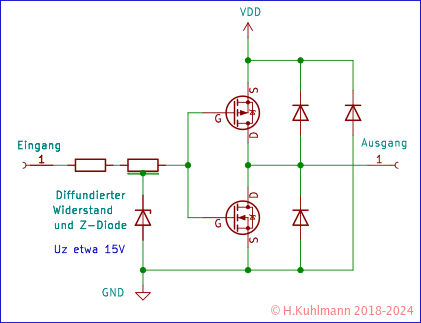

Negative Eingangsspannung

Die Eingänge des 74HC4049 und des CMOS 4049 sind gegen negative Eingangsspannungen geschützt.

Der 74HC4049 und der CMOS 4049 besitzen eine Z-Diode am Eingang, deren Kathode beim 74HC4049 einen Widerstand von ca. 100 Ω und beim CMOS 4049 von ca. 1 kΩ hat.

Durch diese Beschaltung wird der Eingang zwar gegen negative Spannungen geschützt, aber es kann ein Strom fließen, der auf 20 mA begrenzt werden muss.

Negativen Eingangsstrom begrenzen

- Der negative Strom in einen Eingang darf 20 mA nicht überschreiten.

- Die Summe aller negativen Eingangsströme darf 20 mA nicht überschreiten.

Schutz gegen elektrostatische Entladung ESD

Die Ein- und Ausgänge sind gegen elektrostatische Entladung ESD geschützt.

Das Prinzip der Schutzschaltung wird in CMOS- und 74HC-Schutzschaltung beschrieben.

Die Eingänge des 74HC4049 und des CMOS 4049 weichen jedoch, wie oben beschrieben, von der allgemeinen Schutzschaltung ab.

Kein positiver Eingangsstrom

- Die Z-Diode der Eingänge darf nicht als Schutz gegen hohe Eingangsspannungen missbraucht werden.

- Sie dient nur als Schutz vor elektrostatischer Entladung ESD.