74HC74

Der 74HC74 enthält zwei flankengesteuerte D-Register.

Er ist in HCMOS-Technologie gefertigt und für Versorgungsspannungen von 3 V bis 6 V geeignet.

- Allgemeine Daten sind unter Familien digitaler Bauelemente beschrieben.

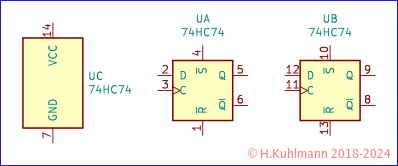

Symbol und Anschlussbelegung

Der 74HC74N hat ein 16-poliges Dual-In-Line-Gehäuse, DIL-Gehäuse.

Die Pinbelegung ist bei allen 74xx74N identisch.

- C ist der Takt-Eingang

- R ist der Reset-Eingang

- S ist der Set-Eingang

- D ist ein Daten-Eingang

- Q ist ein Daten-Ausgang

- Q ist der invertierte Daten-Ausgang von Q

Wahrheitstabelle einer Speicherzelle

| S | R | C | D | Q | Q |

| 0 | 0 | x | x | 1 | 1 |

| 0 | 1 | x | x | 1 | 0 |

| 1 | 0 | x | x | 0 | 1 |

| 1 | 1 | ⭡ | 1 | 1 | 0 |

| 1 | 1 | ⭡ | 0 | 0 | 1 |

| 1 | 1 | 0 | x | Q | Q |

Mit x sind alle Werte (0 oder 1) sowie ⭡ und ⭣ gemeint.

Mit ⭡ ist die Flanke von 0 nach 1 gemeint.

Entsprechend ist mit ⭣ die Flanke von 1 nach 0 gemeint.

Q = NOT Q

1 bedeutet, dass der Zustand instabil und später unbestimmt ist.

Maximale Taktfrequenz

Die maximale Taktfrequenz eines 74HC74 beträgt bei 5 V 21 MHz.

R-S-Register

Wenn der Takt-Eingang CLK eines Registers nicht benutzt wird, also fest auf 0 oder 1 liegt, verhält sich das Register wie ein R-S-Register mit den Eingängen S und R.

Sind gleichzeitig S=0 und R=0, so ist der Zustand Q=1 und Q=1 instabil, d. h., er bleibt nicht erhalten, wenn S=1 und R=1 werden. Der Zustand ist danach unbestimmt.