74HC161 und 74HC162

Der 74HC161 ist ein synchroner 4-Bit-Binärzähler.

Der 74HC162 ist ein synchroner 4-Bit-Dezimalzähler.

Die 74HC161 und 74HC162 haben vier Eingänge für die Daten D0 bis D3 und die Zählerausgänge Q0 bis Q3.

- Allgemeine Daten sind unter Familien digitaler Bauelemente beschrieben.

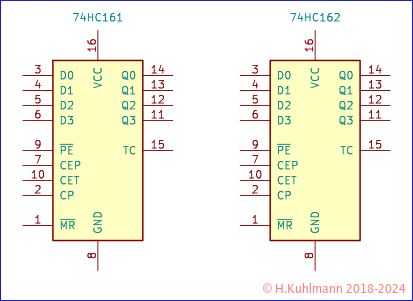

Symbol und Anschlussbelegung

Die 74HC161N und 74HC162N haben 16-polige Dual-In-Line-Gehäuse, DIL-Gehäuse.

Die Pinbelegung ist bei allen 74xx161N und 74xx162N identisch.

Die 74HC161 und 74HC162 besitzen drei synchrone Steuereingänge PE, CEP, CET und den Steuerausgang TC sowie einen asynchronen Reset MR.

| CP | Takt | Positive Flanke ist wirksam, außer beim Master-Reset. |

| PE | Parallel-Enable | Die an den Eingängen D0 bis D3 anliegenden Daten werden übernommen. |

| CEP | Takt-Freigabe-Parallel | Weiterzählen. |

| CET | Takt-Freigabe-Toggle | Weiterzählen und einen eventuellen Überlauf auf TC ausgeben. |

| TC | Toggle-Carry | Überlauf beim Zählen. |

| MR | Master-Reset | Der Zähler wird auf null zurückgesetzt, unabhängig vom Takt. |

Wahrheitstabelle

| Aktion | PE | CEP | CET | CP | MR | D0 - D3 | q0 - q3 | Q0 - Q3 | TC |

| Reset | x | x | x | x | 0 | x | 0 | 0 | 0 |

| Parallel laden | 0 | x | x | ⭡ | 1 | N<15 (N<9) | x | N | 0 |

| Parallel laden | 0 | x | 1 | ⭡ | 1 | N=15 (N=9) | x | N | 1 |

| Zählen | 1 | 1 | 1 | ⭡ | 1 | x | Q<15 (Q<9) | Q+1 | 0 |

| Zählen | 1 | 1 | 1 | ⭡ | 1 | x | Q=15 (Q=9) | 0 | 1 |

| Halten | 1 | x | 0 | x | 1 | x | Q | Q | 0 |

| Halten | 1 | 0 | 1 | x | 1 | x | Q<15 (Q<9) | Q | 0 |

| Halten | 1 | 0 | 1 | x | 1 | x | Q=15 (Q=9) | Q | 1 |

Mit x sind alle Werte (0 oder 1) sowie ⭡ und ⭣ gemeint.

Mit ⭡ ist die Flanke von 0 nach 1 gemeint.

Entsprechend ist mit ⭣ die Flanke von 1 nach 0 gemeint.

Mit 0 1 ⭣ ist 0 oder 1 oder die Flanke von 1 nach 0 gemeint.

A = NOT A

Mit q0 - q3 ist der Zustand der Ausgänge Q0 - Q3 vor dem Takt gemeint.

Mit Q ist der Zählerstand gemeint.

Mit N ist der Wert an den Eingängen D0 - D3 gemeint.

x bedeutet einen beliebigen Wert.

Mit Q=15 ist der Zählerstand 15 des Binärzählers 74HC161,

mit Q=9 ist der Zählerstand 9 des Dezimalzählers 74HC162 gemeint.

Mit Q<15 ist der Zählerstand 0 bis 14 des Binärzählers 74HC161,

mit Q<9 ist der Zählerstand 0 bis 8 des Dezimalzählers 74HC162 gemeint.

Q+1 bedeutet Weiterzählen, und bei Q=15 bzw. Q=9 wird Q+1=0.

Maximale Taktfrequenz

Bei 5 V beträgt die maximale Taktfrequenz des 74HC161 bzw. 74HC162 25 MHz.

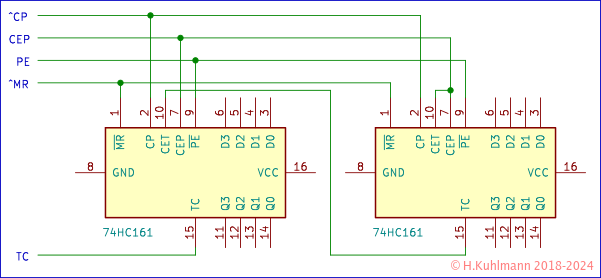

Kaskadierte Zähler

Die Synchronzähler 74HC161 bzw. 74HC162 können in Reihe geschaltet (kaskadiert) werden. Das folgende Schaltbild zeigt das Prinzip.

- Die folgenden Anschlüsse aller kaskadierten Synchronzähler werden parallel geschaltet:

- PE

- CEP

- CP

- MR

- Der Anschluss

- TC wird an

- CET des folgenden Zählers angeschlossen.

- Der 74HC162 wird wie der 74HC161 kaskadiert.

- Kaskadierte 74HC161 bzw. 74HC162 können mit maximal 18 MHz betrieben werden.

- Ansonsten können an den Ausgängen der kaskadierten Zähler Spikes (kurze Impulse) auftreten.

- Werden die 74HC161 bzw. 74HC162 nicht wie oben beschrieben kaskadiert, werden sie asynchron betrieben und an den Ausgängen der hintereinander geschalteten Zähler können Spikes auftreten.