74HC85

Der 74HC85 enthält einen 4-Bit-Binär-Komparator.

Er ist in HCMOS-Technologie gefertigt und für Versorgungsspannungen von 3 V bis 6 V geeignet.

- Allgemeine Daten sind unter Familien digitaler Bauelemente beschrieben.

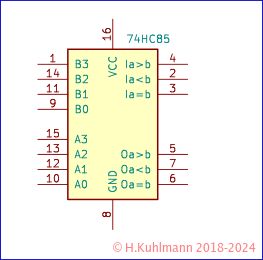

Symbol und Anschlussbelegung

Der 74HC85N hat ein 16-poliges Dual-In-Line-Gehäuse (DIL-Gehäuse).

Die Pinbelegung ist bei allen 74xx85N identisch.

Die Ax und Bx sind die zu vergleichenden Binärwerte.

Ix sind Eingänge für kaskadierte Komparatoren.

Ox sind Ausgänge für kaskadierte Komparatoren.

Logik

Die Binärwerte A und B werden miteinander verglichen und die Ausgänge Oa>b, Oa<b und Oa=b werden entsprechend gesetzt.

Nur wenn A=B (A3=B3, A2=B2, A1=B1 und A0=B0) ist, werden die Eingänge (Ia>b, Ia<b und Ia=b) des vorhergehenden kaskadierten Komparators wirksam.

Wahrheitstabelle

| A3, B3 | A2, B2 | A1, B1 | A0, B0 | Ia>b | Ia<b | Ia=b | Oa>b | Oa<b | Oa=b |

| A3 > B3 | X | X | X | X | X | X | 1 | 0 | 0 |

| A3 < B3 | X | X | X | X | X | X | 0 | 1 | 0 |

| A3 = B3 | A2 > B2 | X | X | X | X | X | 1 | 0 | 0 |

| A3 = B3 | A2 < B2 | X | X | X | X | X | 0 | 1 | 0 |

| A3 = B3 | A2 = B2 | A1 > B1 | X | X | X | X | 1 | 0 | 0 |

| A3 = B3 | A2 = B2 | A1 < B1 | X | X | X | X | 0 | 1 | 0 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 > B0 | X | X | X | 1 | 0 | 0 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 < B0 | X | X | X | 0 | 1 | 0 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | 1 | 0 | 0 | 1 | 0 | 0 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | 0 | 1 | 0 | 0 | 1 | 0 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | 0 | 0 | 1 | 0 | 0 | 1 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | X | X | 1 | 0 | 0 | 1 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | 1 | 1 | 0 | 0 | 0 | 0 |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | 0 | 0 | 0 | 1 | 1 | 0 |

Der Wert X bedeutet, dass er beliebig sein kann.

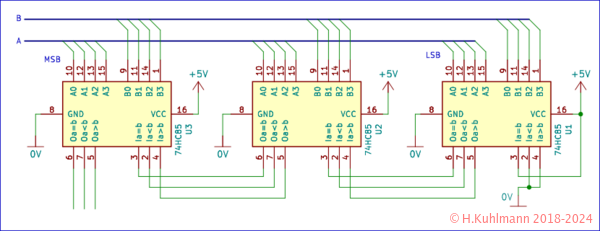

Kaskadieren

Die drei Komparatoren in Bild 2 bilden einen 12-Bit-Komparator. Der Komparator für die niederwertigen Bits (LSB) befindet sich links. Die ausgehenden Vergleichsergebnisse sind mit den eingehenden Vergleichszuständen des nachfolgenden Komparators verbunden. Die eingehenden Vergleichszustände des LSB-Komparators müssen auf Ia>b = 0, Ia<b = 0 und Ia=b = 1 gesetzt werden.