IRF7410

Der IRF7410 ist gegen elektrostatische Entladung empfindlich.

Bitte Vorsicht elektrostatische Entladung beachten.

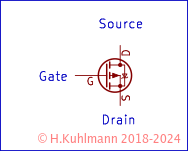

Der IRF7410 ist ein P-Kanal-MOSFET

| Udsmax | Ugsmax | Idmax | Pmax | Rdson | Ugson | Ugsth |

| -12 V | ±8 V | -10 A | 2500 mW | 0,009 Ω | -0,9 V | -0,4 V bis -0,9 V |

| Udsmax | maximal zulässige Drain-Source-Spannung |

| Ugsmax | maximal zulässige Gate-Source-Spannung |

| Idmax | maximal zulässiger Drain-Strom |

| Pmax | maximal zulässige Leistung |

| Rdson | Einschaltwiderstand bei Ugson |

| Ugson | Gate-Source-Spannung für Rdson |

| Ugsth | Gate-Source-Spannung, bei der der MOSFET leitend wird |

| Diese Grenzwerte dürfen nicht überschritten werden. | Siehe: Betriebsdaten und Grenzdaten |

- Der IRF7410 kann als Schalter und Verpolungsschutz eingesetzt werden.

- Der IRF7410 kann von Logik-Systemen ≥ 3 V angesteuert werden.

- Die Gate-Source-Spannung darf ±8 V nicht überschreiten.

- Das Gate des IRF7410 ist nicht gegen höhere Spannungen geschützt.

Symbol

S - Source, D - Drain, G - Gate

Wirkung

Eine negative Spannung Ugs von -2,5 V zwischen Gate und Source schaltet den MOSFET ein. Der Widerstand zwischen Drain und Source ist dann praktisch 0 (etwa 9 mΩ). Der Strom sollte bei Ugs = -2,5 V nicht mehr als -12 A betragen.

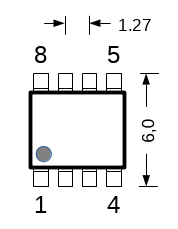

Gehäuse

THT und SMD

Montage von Bauelementen auf Leiterplatten

THT (Through Hole Technology) Durchsteckmontage

- Die Anschlüsse von THT-Bauelementen werden durch Löcher in der Platine gesteckt und von unten verlötet.

- THT-Bauelemente werden auf der Oberseite der Platine montiert.

- Bedrahtete Bauelemente wie Widerstände und Kondensatoren werden in THT montiert. Dazu müssen die Anschlussdrähte entsprechend gebogen werden.

SMD (Surface Mounted Device) Oberflächenmontage

- SMD-Bauelemente benötigen keine Bohrungen, sondern werden direkt auf Kupferpads gelötet.

- SMD-Bauelemente können auf beiden Seiten einer Platine montiert werden.

1 - Source

2 - Source

3 - Source

4 - Gate

5 - Drain

6 - Drain

7 - Drain

8 - Drain

Montage auf Lochrasterplatinen

Das achtpolige SMD-Bauelement des IRF7410 kann auf Lochrasterplatinen montiert werden: SO-Gehäuse.

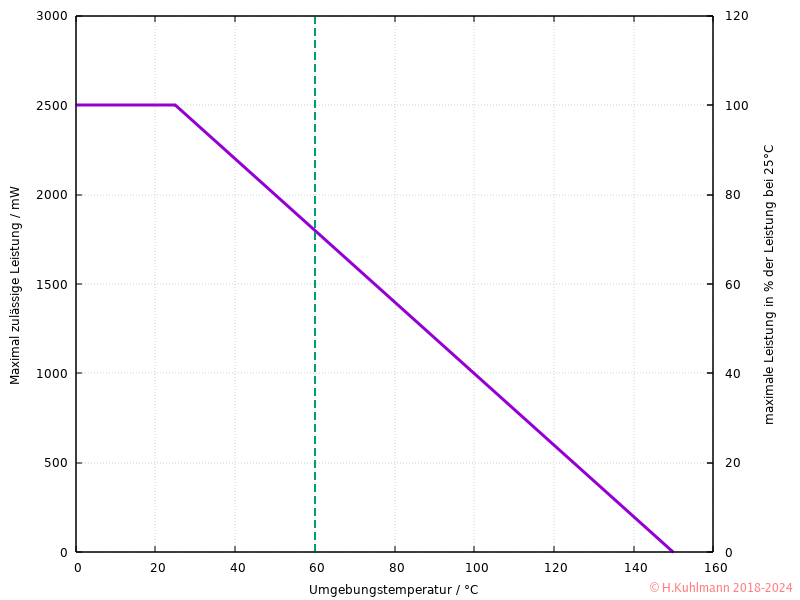

Thermische Eigenschaften

60 °C

Eine maximale Umgebungstemperatur von 60 °C ist für die meisten unserer Anwendungen eine gute Wahl.

- Die maximal zulässige Sperrschichttemperatur des IRF7410 beträgt 150 °C.

- Die maximal zulässige Leistung bei einer Umgebungstemperatur von 25°C ist Pmax=1600 mW.

- Über 25°C Umgebungstemperatur verringert sich die maximal zulässige Leistung um 20 mW/°C.

Das obige Diagramm setzt voraus, dass der IRF7410 auf einer Leiterplatte eingelötet ist.

Die maximal zulässige Verlustleistung kann einfach aus dem Diagramm entnommen werden.

- Wird der IRF7410 mit Leistungen über 75 mW betrieben, ist die Kühlung von SMD-Bauelementen über die Leiterplatte zu beachten.

Regeln

- Der IRF7410 ist empfindlich gegen elektrostatische Entladung.

- Bitte Vorsicht elektrostatische Entladung beachten.

- Die Source des IRF7410 wird an Plus angeschlossen.

- Der IRF7410 wird durch eine negative Spannung zwischen Source und Gate eingeschaltet.

- Die geschaltete Last liegt zwischen Drain und Minus bzw. Masse.

- Das Gate darf niemals offen sein. Ein 1 MΩ-Widerstand ist ausreichend.

- Der IRF7410 schaltet Ströme bis zu -13 A gut, wenn er mit Ugs=-2,5 V angesteuert wird.

- Der IRF7410 darf mit einer maximalen Gate-Source-Spannung von ±8 V betrieben werden.

- Er kann gut mit Spannungen zwischen 3 V und 12 V betrieben werden.

- Das Gate kann direkt mit dem Ausgang eines CMOS-ICs verbunden werden.

- Der IRF7410 verträgt keine hohen Leistungen,

- maximal 1,8 W bei 60 °C Umgebungstemperatur.

Weitere Daten und Kennlinien

- Kennlinien werden im Praktikum Kennlinien beschrieben.

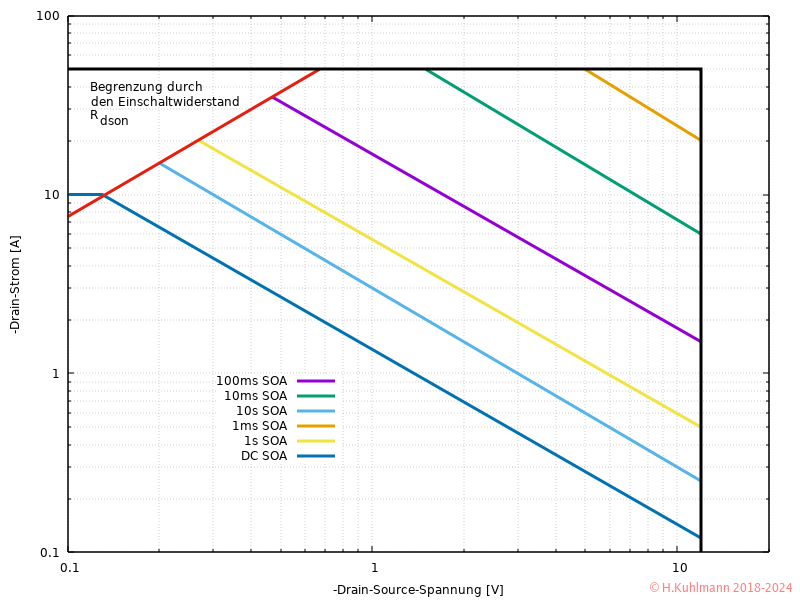

Sicherer Arbeitsbereich (SOA)

Der IRF7410 kann analog mit Gleichstrom betrieben werden: DC SOA.

- Der DC SOA wird nicht vom Hersteller angegeben.

| Id | bei Uds unter |

| -10 A | -0,13 V |

| -0,12 A | -12 V |

- Die Grenzwerte dürfen nur einmalig oder sehr selten überschritten werden. Der IRF7410 darf dauerhaft nur unterhalb des DC-Bereichs betrieben werden.

- Die Daten gelten bei einer Chiptemperatur von 25 °C. Bei höheren Temperaturen muss der Drainstrom Id reduziert werden. Siehe Sicherer Arbeitsbereich (SOA) - Details.

- Der SOA für DC kann entsprechend den %-Angaben rechts im Diagramm für die maximal zulässige Verlustleistung reduziert werden.