Layout für Lochrasterplatinen

Vor dem Aufbau

Der Aufbau auf Leiterplatten ist weitgehend endgültig:

- Eine Korrektur ist aufwendig.

Deshalb sollte eine Schaltung

- auf einem Steckboard getestet werden.

- Auch bevor mit dem Layout begonnen wird.

Im Folgenden konzentrieren wir uns auf die Erstellung des Layouts von Lochrasterplatinen mit dem Entwurfsprogramm KiCad.

- Zunächst wird die Vorgehensweise vorgestellt.

- Diese wird dann an einem praktischen Beispiel erläutert.

- Wir werden uns auch damit beschäftigen, wie SMD-Bauelemente auf Lochrasterplatinen verwendet werden können.

KiCad wurde gewählt, weil

- vier Lagen für die Darstellung benötigt werden und

- KiCad Open-Source und kostenlos ist.

Wir betrachten:

- wie die Verbindungen für Lochrasterplatinen am besten geführt werden,

- wie das Layout für einseitige und beidseitige Lochrasterplatinen erstellt wird,

- wie Drahtbrücken dargestellt werden und

- wie die Seiten der Platine für den Aufbau dargestellt werden.

KiCad für Lochrasterplatinen

- Wir verwenden hier KiCad Version 7.

Es wird vorausgesetzt, dass bereits Grundkenntnisse in KiCad vorhanden sind.

- Eine Einführung wird unter Einführung in KiCad Version 7 und

- unter Deutsche Tutorien auf YouTube gegeben.

- Im Zusammenhang mit der Erstellung von Layouts für Lochrasterplatinen arbeiten wir hier ausschließlich mit Pcbnew, dem Layout-Editor von KiCad.

- Die Darstellung entspricht der Darstellung in KiCad.

- Für Pcbnew wird das Farbschema KiCad Klassisch verwendet. Es ist mit älteren KiCad-Versionen kompatibel.

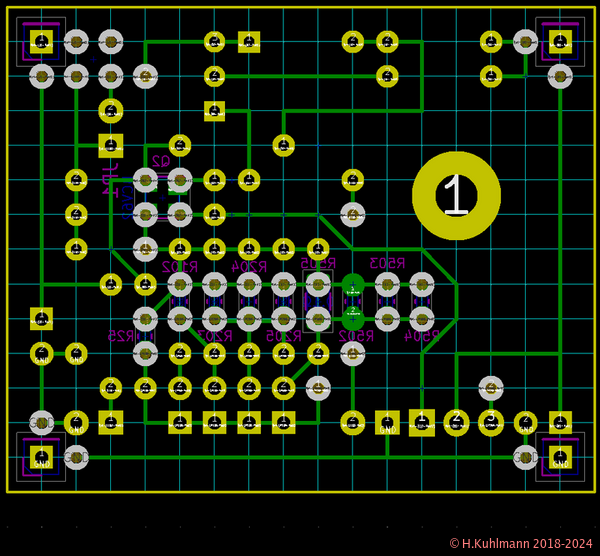

Übersicht

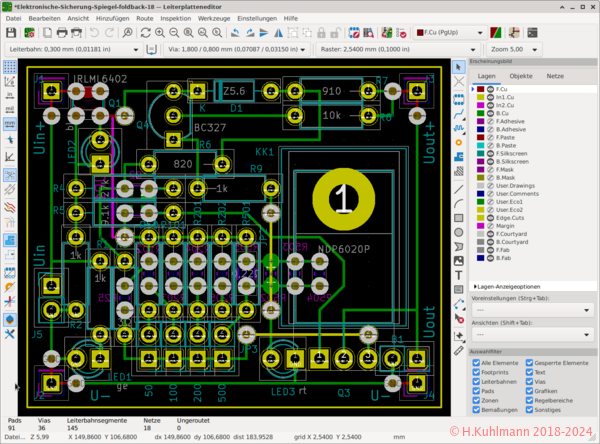

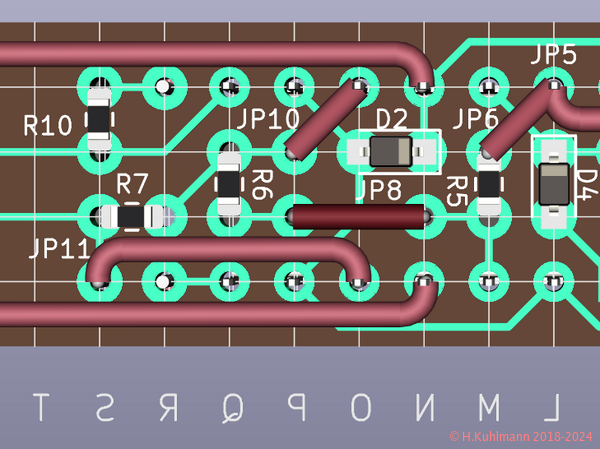

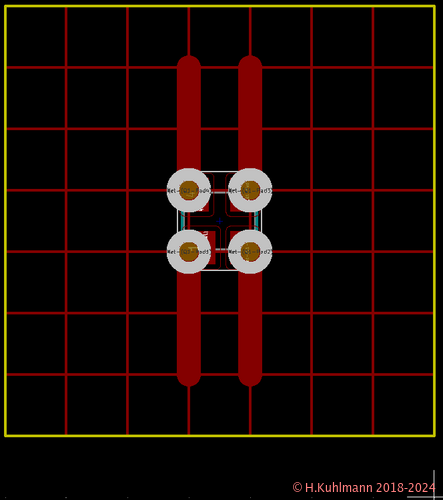

Das Beispiel in Bild 1 fasst die wesentlichen Elemente eines Layouts für Lochrasterplatinen mit KiCad zusammen.

Bauteilfootprints zuweisen

Bevor wir mit dem eigentlichen Layout beginnen, müssen wir festlegen, welche Fußabdrücke (Footprints) wir den Bauelementen zuweisen.

In Eeschema, dem Schaltplaneditor von KiCad, kann im Dialog "Bauteilfootprints zuweisen" jedem Symbol ein Footprint zugewiesen werden.

- Wenn möglich, sollten Footprints mit einem Raster von 2,54 mm verwendet werden.

- Wenn das Bauelement nicht dem 2,54 mm-Raster folgt,

- können geringe Abweichungen (unter 0,5 mm) toleriert werden.

- Bei einigen Bauelementen gibt es Varianten, bei denen die Anschlussdrähte auf ein Raster von 2,54 mm gebogen werden können:

- Diese Möglichkeit besteht natürlich bei Widerständen etc.,

- aber auch für Transistoren im TO-92-Gehäuse, z. B. TO-92_Inline_Wide in der Bibliothek Package_TO_SOT_THT.

- Für SMD-Bauelemente können wir

- die meisten 2-poligen Footprints verwenden: Zweipolige SMD-Gehäuse.

- Nur wenige drei- oder vierpolige SMD-Gehäuse können unmittelbar eingesetzt werden.

- Mehr dazu weiter unten oder unter SOT-Gehäuse und SO-Gehäuse.

- Meist sind Adapterplatinen erforderlich.

Einstellungen in Pcbnew

KiCad

modifiziert im Rahmen seiner Weiterentwicklung das Design seiner Applikationen und Menüs.

Die hier dargestellten Bilder können daher von der aktuellen KiCad-Version abweichen.

Ebenso kann sich die Reihenfolge der Menüs ändern.

Die folgenden Einstellungen in Pcbnew erleichtern die Erstellung eines Layouts für Lochrasterplatinen.

Pcbnew

Pcbnew ist der Layout-Editor von KiCad.

- Leiterbahn: 0,3 mm (0,01181 in)

- Via: 1,800 / 0,800 mm (0,07077 / 0,03150 in)

- Raster: 2,5400 mm (100,00 mils)

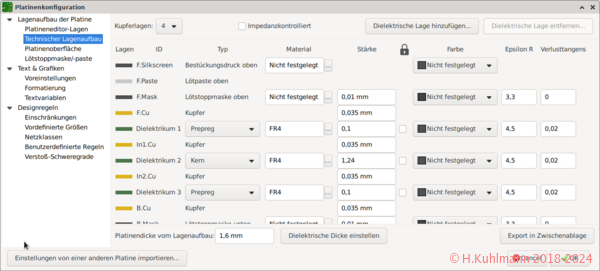

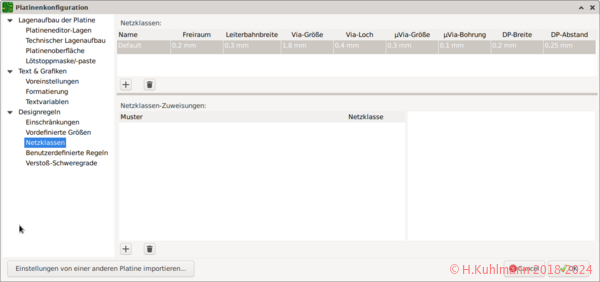

Platinenkonfiguration

- Datei -> Platinenkonfiguration

- Lagenaufbau der Platine -> Technischer Lagenaufbau

- Kupferlagen *4*

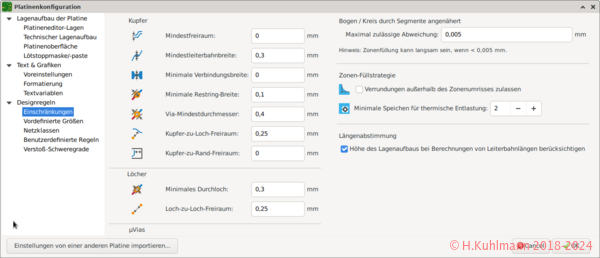

- Designregeln -> Einschränkungen

- Mindestbreite 0,3 mm

- Designregeln -> Vordefinierte Größen

- Unter Leiterbahnen auf + klicken und 0,3 mm eintragen.

- Unter Vias auf + klicken und 1,8 mm und 0,8 mm eintragen.

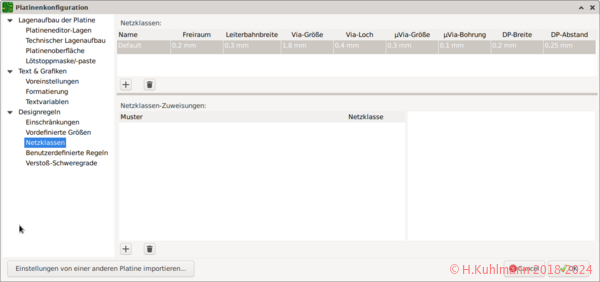

- Designregeln -> Netzklassen

- Default wie in Bild 6

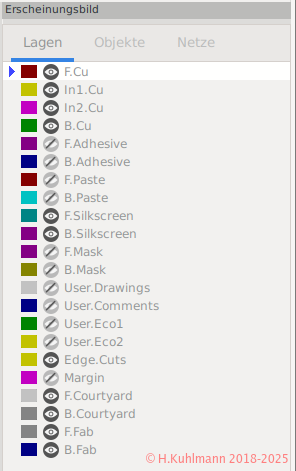

Einstellung der Darstellung

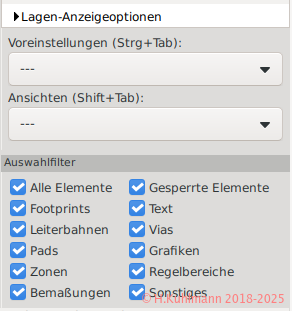

Die wichtigen Einstellungen sind, wie in Bild 2 gezeigt:

- Leiterbahn: 0,3 mm (0,01181 in)

- Via: 1,800 / 0,800 mm (0,07077 / 0,03150 in)

- Raster: 2,5400 mm (100,00 mils)

Außerdem ist es hilfreich,

- das Hintergrundraster zu aktivieren und

- mm zu verwenden.

Im Layout sind eine ganze Reihe von Informationen zunächst überflüssig und sollten ausgeschaltet werden.

Auf der rechten Seite unter Erscheinungsbild -> Lagen sollten die Lagen wie im folgenden Bild 7 aktiviert werden.

- Für das Layout werden die Raster F.Paste und B.Paste nicht benötigt. Später können sie zur Darstellung des Rasters verwendet werden.

- Die Größe der Leiterplatte sollte, wenn bekannt, als Edge.Cuts dargestellt werden.

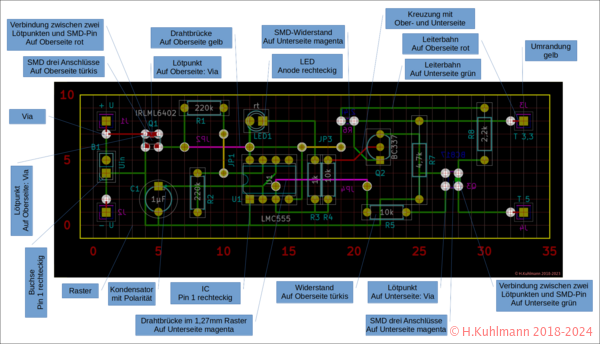

Zuordnung der Layer

- Die Leitungen auf der Unterseite werden als B.Cu grün dargestellt.

- Die Leitungen auf der Oberseite werden als F.Cu rot dargestellt.

- Drahtbrücken auf der Oberseite werden als In1.Cu gelb dargestellt.

- Drahtbrücken auf der Unterseite werden als In2.Cu magenta dargestellt.

- Die Größe der Leiterplatte wird als Edge.Cuts gelb dargestellt.

- Vias werden als hellgraue (hellgrau) Kreise mit einem weißen Punkt in der Mitte dargestellt.

Routing

- Vias werden als 1,8 mm Lötpunkte mit 0,8 mm Bohrungen dargestellt.

- Verbindungen haben eine Breite von 0,3 mm.

- Verbindungen sollten möglichst auf der Unterseite (B.Cu) hergestellt werden.

- Verbindungen auf der Oberseite (F.Cu) möglichst vermeiden.

- Verbindungen auf der Oberseite (F.Cu) liegen bei durchkontaktierten Platinen parallel zu Verbindungen der Unterseite (B.Cu). Sie werden kurzgeschlossen.

- Für Drahtbrücken auf der Oberseite immer In1.Cu verwenden.

- Verbindungen auf der Oberseite (F.Cu) sind sinnvoll,

- wenn SMD-Bauelemente auf der Oberseite montiert werden und

- bei beengten Platzverhältnissen zwei Leitungen auf der Oberseite geführt werden.

- Auf der Unterseite (B.Cu) sind möglichst rechtwinklige Verbindungen zu verwenden, da sie sich leichter löten lassen.

- SMD-Bauelemente werden auf/zwischen Lötpunkten im 2,54 mm-Raster gesetzt.

- Die Anschlüsse von SMD-Bauelementen werden als Vias dargestellt.

- Drahtbrücken In1.Cu und In2.Cu dürfen nicht über Bauelemente geführt werden.

- Drahtbrücken werden mit isoliertem Draht erstellt und dürften über Vias geführt werden.

- Pcbnew verbindet dann aber die Vias mit der Drahtbrücke.

- Drahtbrücken werden in Pcbnew am besten neben Vias geführt (Raster 1,2700 mm 50,00mils).

- Manchmal ist es sinnvoll, eine Drahtbrücke gerade über Lötpunkte von SMD-Bauelementen zu führen.

- Dann dürfen die Anschlüsse der SMD-Bauelemente nicht als Vias dargestellt werden.

- Drahtbrücken beginnen und enden auf eigenen Vias.

- Drahtbrücken sollten nur in Ausnahmefällen mit Anschlüssen auf der Unterseite verbunden werden,

- weil sie kaum lötbar sind und

- schon gar nicht auf der Oberseite.

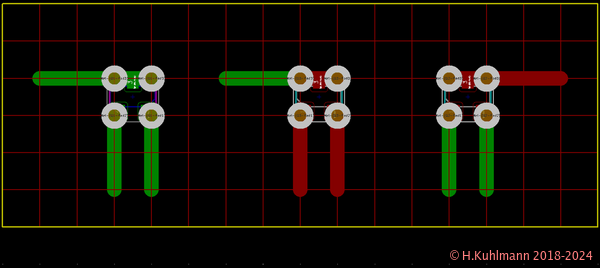

Sonderfälle

Bei beengten Platzverhältnissen können

- Drahtbrücken direkt an die Anschlüsse von Bauelementen angeschlossen werden und

- Kreuzungen auf der Ober- und Unterseite erstellt werden – siehe (20,6) in Bild 1.

- Falls mehr als eine Drahtbrücke auf der Oberseite bzw. Unterseite erforderlich ist,

- können sie natürlich mit isoliertem Draht parallel liegen bzw. sich kreuzen.

- Die zweite Drahtbrücke wird im Layout als normale Verbindung

- auf der Oberseite als (F.Cu) oder

- auf der Unterseite als (B.Cu),

aber mit einem Abstand von 1,27 mm zwischen den Lötpunkten geführt.

- Oben zwischen O und P bzw. L und M liegen Kreuzungen.

- In der oberen Reihe wurden Drahtbrücken unmittelbar an Anschlüsse von Bauelementen geführt.

- In der unteren Reihe liegen zwei parallele Verbindungen zwischen L und P.

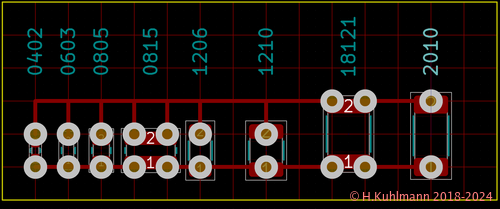

SMD

SMD-Bauelemente passen nicht in das 2,54 mm-Raster der Lochrasterplatinen.

Nur zweibeinige und einige drei- oder vierbeinige SMD-Bauelemente können unmittelbar eingelötet werden.

Für alle anderen SMD-Gehäuse werden am besten Adapter verwendet.

Zweibeinige SMD-Bauelemente

- Zweibeinige SMD-Bauelemente wie Widerstände können einfach auf zwei Lötpunkte gesetzt werden.

Widerstände in SMD-Gehäusen können einfach auf zwei Lötpunkte gesetzt werden.

SOT-23-Gehäuse

SMD-Bauelemente mit vier Anschlüssen können auf vier benachbarte Lötpunkte gesetzt werden.

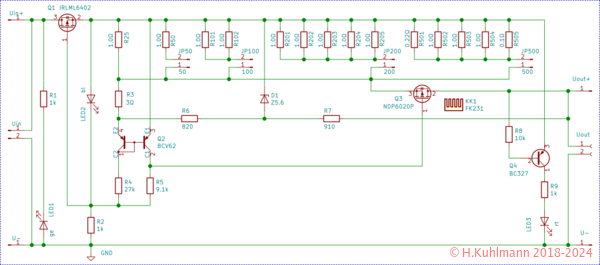

Beispiel

Das Projekt Elektronische Sicherung für Spannungen bis 18 V - begrenzend ist ein gutes Beispiel.

Die Schaltung ist nicht sehr komplex. Der Aufbau und das Layout enthalten jedoch alle Elemente, die wir hier betrachten wollen.

- Es wird eine durchkontaktierte Lochrasterplatine verwendet.

- Die Schaltung ist ein Modul für Steckboards mit auf der Unterseite eingebauten einzelnen Stiften.

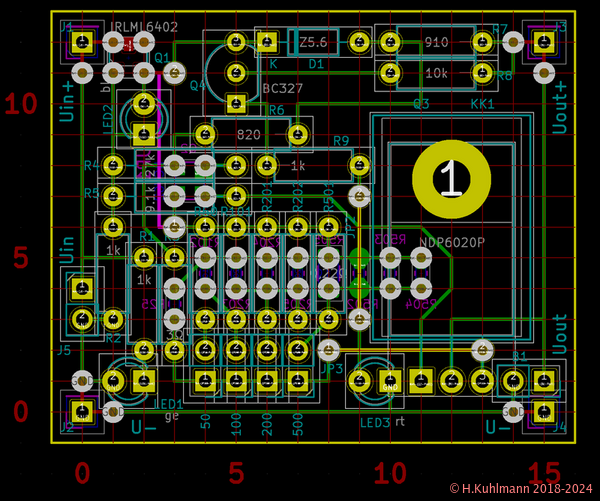

Das Layout

Lagen anzeigen

In Pcbnew können die angezeigten Lagen über das Menü unten rechts eingestellt werden. Über den Knopf unter Voreinstellungen können die angezeigten Lagen ausgewählt werden.

Layout der Oberseite

Das Layout der Oberseite in Bild 14 zeigt die Lage der auf der Oberseite montierten Bauelemente.

Die Verbindungen zu den vier Stiften befinden sich auf der Oberseite in F.Cu.

Der SMD-MOSFET Q1 befindet sich auf der Oberseite, seine Anschlüsse und Verbindungen sind F.Cu.

Für den Transistor Q4 wird der Footprint TO-92_Inline_Wide verwendet.

Die Vias für die Stifte und den MOSFET Q1 sind dargestellt.

Die Drahtbrücke JP3 kann über Lötpunkte der Platine geführt werden, da keine Vias im Weg sind. Die Drahtbrücke wird unter den Anschlüssen des MOSFET Q3 hindurchgeführt.

Die Drahtbrücke JP2 kann nur deshalb direkt geführt werden, weil die Lötpunkte R502 nicht als Vias dargestellt sind.

Die Bezeichner und die Werte der Bauelemente sind grau und türkis dargestellt.

Das Raster von 2,54 mm in F.Paste mit einer Breite von 0,05 mm ist hilfreich beim Aufbau der Schaltung.

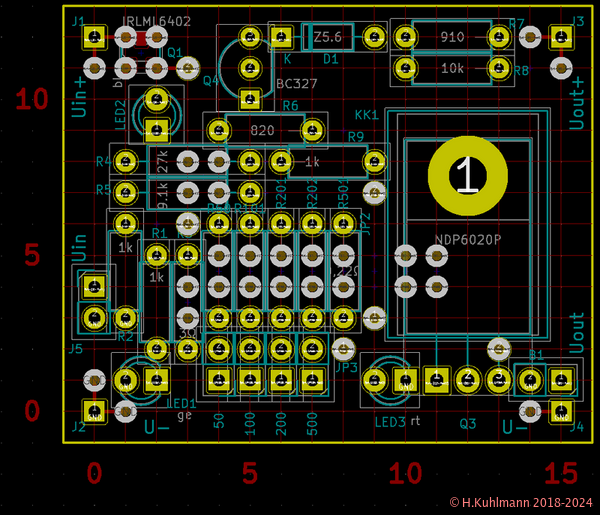

Layout der Unterseite

Bild 15 zeigt das Layout der Unterseite.

Zur Orientierung ist ein Raster von 2,54 mm in B.Paste mit 0,05 mm Breite eingetragen.

Die Leiterbahnen auf der Unterseite sind natürlich B.Cu.

Die Drahtbrücke JP1 ist In2.Cu. Sie würde über Lötpunkte mit Anschlüssen führen. Das ist zwar mit isoliertem Draht möglich, aber Pcbnew würde eine Verbindung annehmen. Daher ist die Brücke JP1 mit einem Raster von 1,27 mm (50mils) eingetragen worden.

Die SMD-Bauelemente, der Doppeltransistor Q2 und die Widerstände werden einfach zwischen vier bzw. zwei Lötpunkten mit Vias gesetzt.

Gesamtes Layout

Das Layout in Bild 13 ist eine Zusammenfassung der Layouts der Ober- und Unterseite.

Es ist die Arbeitsansicht in Pcbnew.

Bei der Erstellung des Layouts ist das in F.Mask und B.Mask dargestellte Raster oft störend und wird meist abgeschaltet.

- Das Raster und dessen Nummerierung müssen selbst erstellt werden, KiCad generiert sie nicht automatisch.

Dreidimensionale Darstellung

Wozu 3-D

Für den Entwurf des Layouts und den Aufbau einer Schaltung ist die 3-D-Darstellung nicht erforderlich.

Sie ist hilfreich, um eine Vorstellung von der fertigen Platine zu bekommen.

Dazu müssen nicht alle Bauelemente in 3-D dargestellt werden. Insbesondere Drahtbrücken werden nicht benötigt.

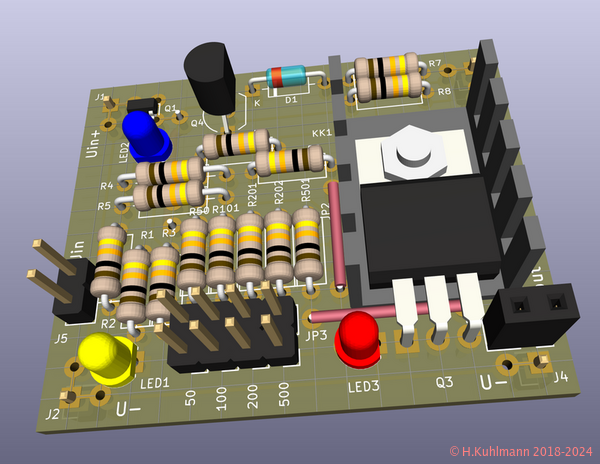

Oberseite in 3-D

Bild 16 zeigt die Oberseite in 3-D. Auf der Oberseite befinden sich einige Bauelemente:

- Widerstände

- drei LEDs

- eine Z-Diode

- zwei Steckleisten

- eine Steckbuchse

- zwei Drahtbrücken

- ein Transistor im TO-92-Gehäuse

- ein MOSFET im TO-220-Gehäuse auf einem Kühlkörper

- ein MOSFET im SMD-Gehäuse

Oben links ist der MOSFET mit seinem dreipoligen SMD-Gehäuse auf vier Lötpunkte gesetzt. Der dritte Anschluss ist mit einem Draht verbunden, der weiter zu einem Stift führt. Die unteren Lötpunkte werden als Vias verwendet.

Die Anschlüsse der SMD-Bauelemente (oben und unten) werden meist als Vias dargestellt.

Die Anschlüsse des SMD-Widerstands R502 sind nicht als Vias dargestellt. Dadurch kann die oben liegende Drahtbrücke JP2 gerade über die Anschlüsse von R502 geführt werden. Die Drahtbrücke JP2 wird später mit isoliertem Draht hergestellt.

An den vier Ecken befinden sich die von unten eingebauten Einzel-Stifte einer Stiftleiste. Diese sind auf der Oberseite verlötet und mit Vias verbunden.

Die Drahtbrücken werden wie THT-Bauelemente eingebaut.

Die in 3-D gezeigten Drahtbrücken sind im Layout nicht vorhanden und werden hier als spezielle Bauelemente dargestellt.

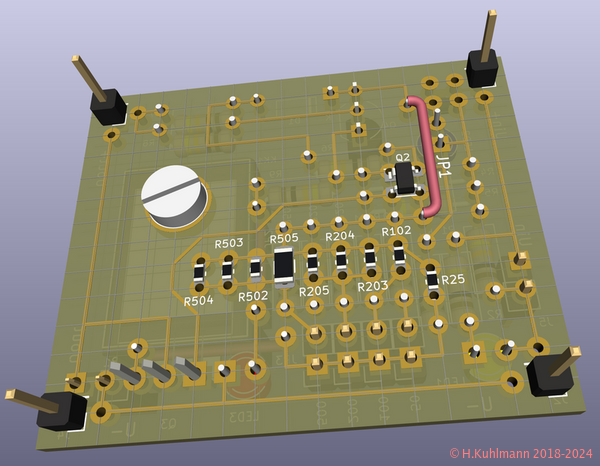

Unterseite in 3-D

Bild 17 zeigt die Unterseite in 3-D. Auf der Unterseite befinden sich einige Bauelemente:

- der vierpolige Doppeltransistor Q2,

- einige SMD-Widerstände,

- die vier Stifte und

- eine Drahtbrücke.

Der größte Teil der Verdrahtung befindet sich auf der Unterseite.

Der vierpolige Doppeltransistor im SMD-Gehäuse liegt auf vier Lötpunkten, die SMD-Widerstände auf zwei.

Die beiden Vias für den MOSFET Q1 sind oben rechts zu erkennen, ebenso wie die Vias für die SMD-Widerstände.

Die von unten eingebauten Einzel-Stifte müssen auf der Oberseite verlötet und verbunden werden.

Die Drahtbrücken werden wie THT-Bauelemente eingebaut, jedoch von unten.

Die in 3-D gezeigten Drahtbrücken sind im Layout nicht vorhanden und werden hier als spezielle Bauelemente dargestellt.

Layout in 3-D darstellen

Eigentlich ist es ganz einfach, in KiCad ein Layout in 3-D darzustellen.

- In Pcbnew Ansicht -> 3D-Betrachter anklicken

- Im 3-D-Betrachter wird:

- mit dem Scrollrad skaliert,

- mit der linken Maustaste gedreht und

- mit der mittleren verschoben.

Voraussetzung

- Für viele Bauelemente sind in KiCad 3-D-Modelle hinterlegt.

- Diese selbst zu erstellen, ist recht aufwendig:

- Das 3-D-Modell wird in einem 3-D-Zeichenprogramm wie z. B. FreeCAD erstellt und

- im KiCad Footprint-Editor unter

Datei -> Footprint-Eigenschaften -> 3-D-Modelle

eingefügt, positioniert und skaliert.