Delta-Sigma-Digital-Analog-Wandler

Der Delta-Sigma-Digital-Analog-Wandler ist ein weiterer 1-Bit-Digital-Analog-Wandler. Er erzeugt eine Folge von Impulsen, die über die Zeit gemittelt eine Spannung ergeben, die dem gewandelten Binärwert entspricht. Der Delta-Sigma-DAC gibt nicht, wie die Pulsweiten-Wandler nur einen Impuls pro Periode aus, sondern eine Folge von kurzen, meist gleich langen Impulsen aus.

Für eine solche Folge von Impulsen kann der Mittelwert auf einfache Weise gebildet und geglättet werden.

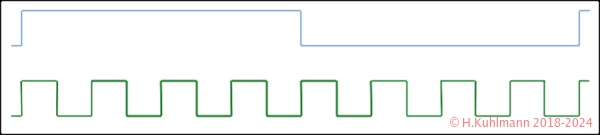

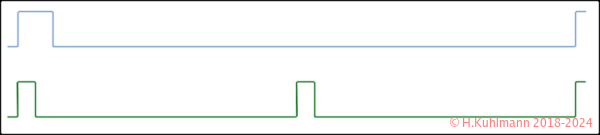

Bild 1 zeigt einen Vergleich zwischen Pulsweite und Delta-Sigma. Bei einer Periode von 16 entspricht der Wert 8 einem Impuls der Breite 8 oder 8 Impulsen der Breite 1.

Ein Delta-Sigma-DAC erzeugt eine Folge von Impulsen, die leichter gemittelt werden können als bei einem Pulsweiten-DAC.

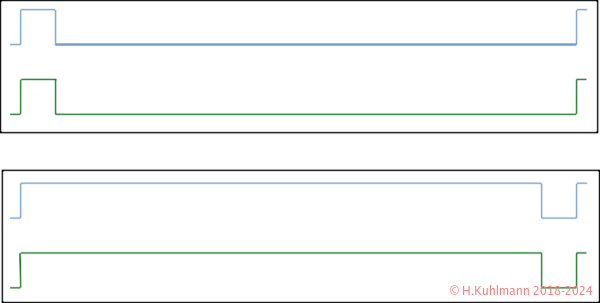

- Dies ist in den meisten Fällen der Fall, aber nicht immer:

- Für den Binärwert 00000...0001 oder 11111...1110 wird nur ein Impuls pro Periode erzeugt.

Das Prinzip des Delta-Sigma-DAC

Ein Binärwert, der gewandelt werden soll, wird mit einer hohen Taktfrequenz untersucht, die etwa der Frequenz entspricht, mit der ein Pulsweiten-Wandler arbeitet.

Wir untersuchen, wie viele Impulse pro Periode mit einer Länge von Bmax Takten ausgegeben werden müssen. Wenn der aktuelle Binärwert Bin ist, sind dies Bin Impulse pro Periode, also Bin / Bmax.

Wenn wir die Impulse gleichmäßig über die Periode verteilen wollen, müssen wir alle Bmax / Bin Takte einen Impuls ausgeben.

Die Division Bmax / Bin ist natürlich zu kompliziert.

Um Bmax / Bin zu berechnen, müssen wir nur zählen, wie oft Bin in Bmax passt.

Das ist nichts anderes als eine Folge von Additionen und Vergleichen.

- Wir beginnen bei 0 und addieren pro Takt Bin dazu, bis wir Bmax erreicht haben.

- Dann geben wir einen Impuls aus und fangen wieder von vorne an.

Dieses Verfahren ist nur dann korrekt, wenn Bmax durch Bin teilbar ist. Das folgende Verfahren berücksichtigt auch den Rest der Division.

Bakt ist der Akkumulator für die fortlaufende Addition. In ihm werden die Werte von Bin aufsummiert. Der Akkumulator muss den Wert des vorhergehenden Takts zwischenspeichern.

Bakt := Bakt + Bin bedeutet, dass Bakt durch einen neuen Wert ersetzt wird.

- Wir beginnen mit Bakt = 0.

-

Bei jedem Takt wird Bin zu Bakt addiert:

Bakt := Bakt + Bin .

- Wenn der neue Wert von Bakt kleiner als Bmax ist, geben wir eine 0 aus.

- Wenn der neue Wert von Bakt gleich oder größer als Bmax ist, geben wir eine 1 aus und subtrahieren Bmax von Bakt, also Bakt := Bakt - Bmax.

Auf diese Weise werden auch die Fälle abgedeckt, in denen Bmax nicht durch Bin teilbar ist: Der Rest verbleibt in Bakt und wird im nächsten Takt berücksichtigt.

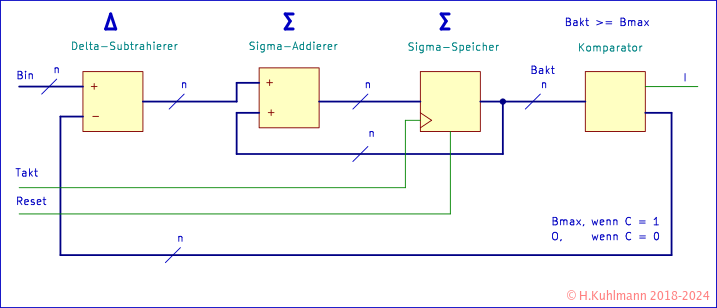

Der Delta-Sigma-DAC benötigt einen Addierer mit Speicher, einen Komparator und einen Subtrahierer.

Delta-Sigma

Der Addierer bildet zusammen mit dem Speicher den Summierer Bakt . Bei jedem Takt wird ein Wert zum Summierer addiert.

Dieser Wert ist entweder Bin oder Bin - Bmax .

Der Komparator bestimmt, welcher Wert genommen wird:

Ist Bakt >= Bmax, wird Bin - Bmax genommen, sonst Bin.

Ein Delta-Sigma-DAC besteht aus drei Elementen:

- einem Subtrahierer Δ,

- einem Summierer Σ und

- einem Komparator.

Der Subtrahierer subtrahiert den vom Komparator gelieferten Wert (0 oder Bmax) von Bin .

Der Summierer ist ein Addierer mit Speicher. Er addiert die vom Subtrahierer gelieferten Werte.

Der Komparator entscheidet, ob der Wert Bakt >= Bmax ist und liefert den Wert C sowie 0 oder Bmax .

Der Name Delta-Sigma-Wandler kommt daher, dass:

- am Eingang des Wandlers eine Differenz gebildet wird: Delta Δ

- und anschließend summiert wird: Sigma Σ

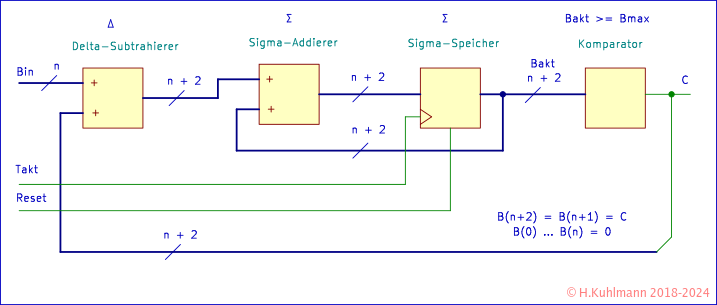

Ein Subtrahierer ist kein Standardbauteil. Wir könnten einen Addierer verwenden, wenn der zweite Eingang -Bmax ist.

Das ist relativ einfach, wenn der Addierer mehr als n Bits hat. Dann ist der negative Wert von Bmax eine Konstante.

Meist werden zwei zusätzliche Bits, wie in Bild 4, verwendet.

Beispiel für n=4

Bmax = 010000 invertiert 101111 +1 1 -Bmax = 110000

Wenn wir für Bmax den maximal möglichen Wert einer n-stelligen Binärzahl nehmen, bekommen wir den Komparator umsonst, nämlich den Überlauf-Ausgang des Addierers.

Oh, Überlauf!

Dann verwirft der Addierer den maximal möglichen Wert einer n-stelligen Binärzahl, d. h. Bmax wird automatisch subtrahiert.

Den Subtrahierer brauchen wir nicht.

Wir brauchen nur:

- einen Addierer und

- einen Speicher.

Die Genauigkeit eines Delta-Sigma-DACs ist abhängig von der maximalen Anzahl 2n der Impulse pro Periode, d. h. von den Bits des Addierers für Bakt und des zugehörigen Speichers.

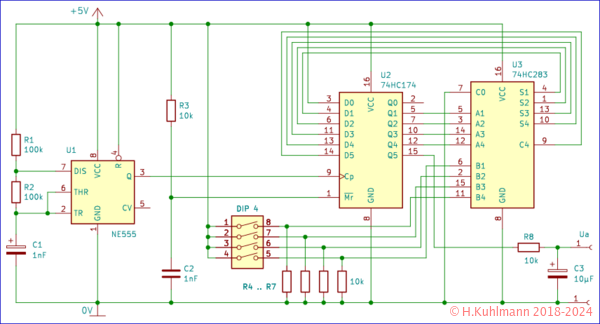

4-Bit-Delta-Sigma-DAC für eigene Versuche

Die wesentlichen Elemente sind der 4-Bit-Volladdierer 74HC283 und das 6-fach-D-Register 74HC174. Das 6-fach-D-Register speichert den aktuellen Wert von Bakt in D1 bis D4. Der Überlauf-Ausgang des 4-Bit-Volladdierers wird in D5 gespeichert. Dadurch wird eine Änderung des Eingangswertes nicht sofort an den Ausgang weitergegeben. Am Ausgang steht also nicht der Wert des Komparators, der dem aktuell gespeicherten Eingangswert entspricht, sondern der vorhergehende Wert.

Der Eingangswert wird mit dem DIL-Schalter eingestellt.

Die Ausgangsspannung des 1-Bit-Ausgangs des Delta-Sigma-DACs wird über R8 und C3 gemittelt.

Der Taktgenerator erzeugt eine Frequenz von 4,8 kHz. Um die Impulsfolge am Ausgang des Komparators (C4 oder D5) verfolgen zu können, kann z. B. der Kondensator C1 durch einen Kondensator mit 10 µF ersetzt werden.

Oversampling

Oversampling bedeutet Überabtastung.

Moderne Delta-Sigma-DACs verwenden fast immer Oversampling. Damit ist gemeint, dass die Breite des Addierers Bakt, des Speichers usw. größer ist als die Breite des zu wandelnden Wertes.

Konkret ist Oversampling der Faktor Os, mit dem die Anzahl der Impulse pro Periode multipliziert wird.

Bei einem Oversampling von zwei werden beispielsweise doppelt so viele Impulse pro Periode ausgegeben wie ohne Oversampling.

Bild 6 zeigt einen Vergleich zwischen Pulsweite und Delta-Sigma mit Oversampling 2. Für den Wert 1 werden bei Delta-Sigma mit Oversampling zwei Impulse pro Periode ausgegeben. Ohne Oversampling wäre es nur ein Impuls (Bild 2).

In der Praxis bedeutet dies, dass der Delta-Sigma-DAC um einige Bits erweitert wird: n zusätzliche Bits führen zu einem Oversampling von Os = 2n.

Dies hat zur Folge, dass

- die Taktfrequenz des Delta-Sigma-DACs dann Os mal so hoch ist,

- der Eingangswert Os mal an den Delta-Sigma-DAC übergeben wird.

Das Oversampling erhöht natürlich den Rechenaufwand, stellt aber für moderne ICs kein Problem dar.

Der analoge Teil, die Glättung der Impulsfolge des 1-Bit-Delta-Sigma-DACs, wird dadurch einfacher.

Bei modernen Delta-Sigma-DACs für Audioanwendungen mit 16 Bit Breite ist ein Oversampling von 256 üblich, d. h. es wird mit 24 Bit gearbeitet.