CMOS-Gatter

Gatter

In diesem Praktikum betrachten wir eine Reihe von Schaltungen mit Transistoren.

Wir konzentrieren uns auf einfache logische Schaltungen, die Gatter genannt werden.

Es ist von Vorteil, wenn vorher einige Praktika der Digitaltechnik durchgeführt wurden.

Wir verwenden positive Logik:

- Eine logische 1 ist eine positive Spannung von etwa 5 V.

- Eine Spannung in der Nähe der positiven Versorgungsspannung wird als HIGH bezeichnet.

- Der Spannungsbereich von HIGH hängt von der verwendeten Technologie ab.

- Bei 5 V können wir davon ausgehen, dass HIGH über 4 V sicher erkannt wird.

- Die logische 0 entspricht etwa 0 V.

- Eine Spannung unter 0,8 V wird als LOW bezeichnet.

CMOS bedeutet Complementary MOSFET, komplementäre MOSFETs.

Wir betrachten zunächst, wie CMOS-Inverter aufgebaut sind und wie sie funktionieren. Anschließend wird anhand von NOR- und NAND-Gattern gezeigt, wie Gatter in CMOS-Technologie aufgebaut sind.

CMOS-Inverter

Den CMOS-Inverter 4049 kennen wir aus dem Digital-Praktikum Was heißt denn hier EINS, in dem wir die verschiedenen Logikzustände betrachtet haben.

Es gibt zwei große Familien von CMOS-Bausteinen.

- Die Standard-CMOS-Familie für 3 V bis 15 V Betriebsspannung, die hier als CMOS bezeichnet wird.

- Die 74HC-Familie für 2 V bis 6 V Betriebsspannung, die hier als 74HC bezeichnet wird.

Wir betrachten beide Varianten des 4049, den CMOS 4049 und den 74HC4049.

Die interne Schaltung der beiden Varianten des Inverters unterscheidet sich kaum, sondern eher in den Eigenschaften der verwendeten MOSFETs.

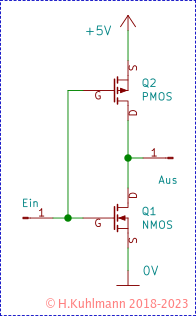

Die Schaltung eines CMOS-Inverters haben wir bereits in Komplementäre Transistoren betrachtet.

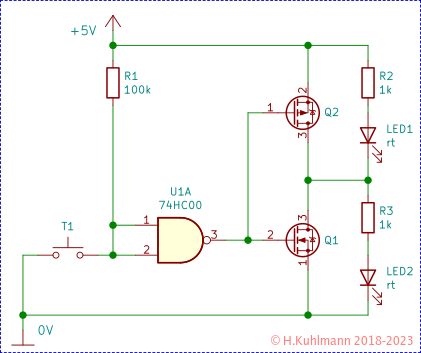

In Bild 1 sind die Gates und die Drains zweier komplementärer MOSFETs miteinander verbunden. An den gemeinsamen Ausgang ist die Last, zwei LEDs, angeschlossen. Bei logisch 1, HIGH (+5 V) an den Gates leitet Q1, und LED1 leuchtet. Bei einer logisch 0, LOW (0 V) leitet Q2, und LED2 leuchtet. Es leitet immer nur einer der beiden MOSFETs. Die Spannung an den Gattern der beiden MOSFETs ist entweder HIGH oder LOW, d. h., es ist immer einer der beiden MOSFETs leitend.

Wenn die Last, die beiden LEDs am Ausgang entfernt wird, fließt kein Strom durch die beiden MOSFETs. Dennoch ist der Zustand am Ausgang eindeutig: Entweder ist er logisch 0, wenn Q1 leitet, oder logisch 1, wenn Q2 leitet.

Ein Gatter eines CMOS 4049 oder 74HC4049 würde diesen Zustand eindeutig erkennen.

Die Schaltung in Bild 1 hat die Digitaltechnik geradezu revolutioniert. Die Schaltung entspricht prinzipiell einem Inverter im 4049.

Wie sich die Schaltung in Bild 2 verhält, haben wir im Prinzip in Bild 1 beschrieben.

Kennlinie eines 4049-Inverters

Das Verhalten eines CMOS-Inverters lässt sich am besten durch Kennlinien beschreiben.

Wir betrachten die Wirkung der Eingangsspannung eines CMOS-Inverters.

- Welche Ausgangsspannung liefert der Inverter in Abhängigkeit von der Eingangsspannung?

- Welcher Strom fließt durch den Inverter in Abhängigkeit von der Eingangsspannung?

- Wie unterscheiden sich die Ausgangsspannungen eines CMOS 4049 und eines 74HC4049?

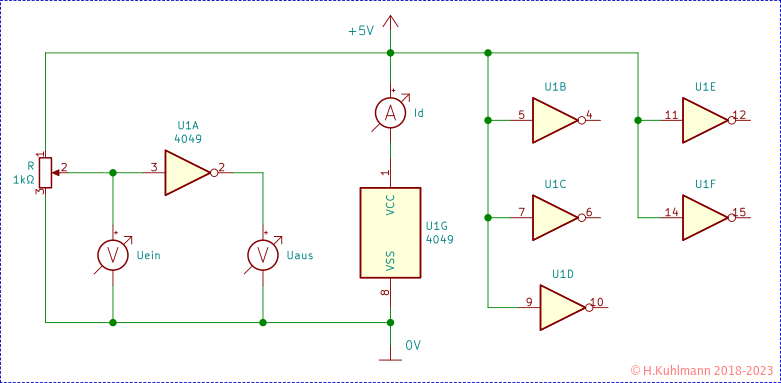

Mit der Schaltung in Bild 3 können wir die Kennlinie eines 4049-Inverters aufnehmen. Damit die anderen Inverter im 4049 keinen Einfluss haben, haben wir die Eingänge auf +5 V gelegt.

Die Eingangsspannung wird mit einem Potentiometer eingestellt und die Ausgangsspannung gemessen.

Den Strom durch einen Inverter können wir nicht direkt messen. Der Strom in der Versorgungsleitung des 4049 ist natürlich der Strom durch alle sechs Inverter. Bei einer Eingangsspannung von +5 V ist dieser Strom sehr klein. Wenn der Strom ansteigt, fließt er nur durch den gemessenen Inverter. Der Strom in den anderen Invertern kann vernachlässigt werden.

Wir nehmen die Kennlinien eines CMOS 4049 und eines 74HC4049 auf.

Wir nehmen die Ausgangsspannung bei verschiedenen Eingangsspannungen auf und tragen sie in eine gemeinsame Tabelle ein.

| Uein / V | CMOS Uaus / V |

74HC Uaus / V |

| 0.0 | 5.00 | 5.00 |

| 0.5 | 5.00 | 5.00 |

| 1.0 | 5.00 | 5.00 |

| 1.5 | 5.00 | 5.00 |

| 2.0 | 4.84 | 5.00 |

| 2.5 | 0.27 | 1.89 |

| 3.0 | 0.06 | 0.01 |

| 3.5 | 0.01 | 0.01 |

| 4.0 | 0.01 | 0.01 |

| 4.5 | 0.01 | 0.01 |

| 5.0 | 0.01 | 0.01 |

Tabelle 1

Offensichtlich ändern sich die Ausgangsspannungen bei Eingangsspannungen um 2,5 V stark.

Wir messen zwischen 1,8 V und 2,9 V genauer:

| Uein / V | CMOS Uaus / V |

74HC Uaus / V |

| 1.8 | 4.95 | 5.00 |

| 1.9 | 4.90 | 5.00 |

| 2.0 | 4.84 | 5.00 |

| 2.1 | 4.72 | 5.00 |

| 2.2 | 4.56 | 5.00 |

| 2.3 | 4.26 | 5.00 |

| 2.4 | 2.54 | 4.16 |

| 2.5 | 0.27 | 1.45 |

| 2.6 | 0.18 | 0.02 |

| 2.7 | 0.14 | 0.01 |

| 2.8 | 0.10 | 0.01 |

| 2.9 | 0.07 | 0.01 |

Tabelle 2

Zur korrekten Darstellung der Kennlinien müssen diese Werte in Tabelle 1 in der richtigen Reihenfolge eingetragen werden.

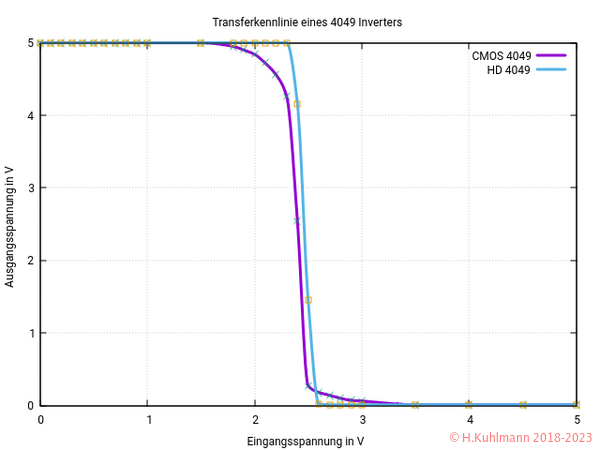

Diese Kennlinien werden Transferkennlinien genannt, weil sie die Übertragung zwischen Eingangs- und Ausgangsspannung darstellen.

Es ist ersichtlich, dass die Ausgangsspannung ihren Pegel in einem relativ engen Bereich der Eingangsspannung zwischen 2 V und 3 V, etwa bei 2,5 V, ändert. Dies ist bei beiden Familien gleich, obwohl die Kennlinie des 74HC4049 steiler ist.

- Zwischen 0 V und 1 V ist der P-MOSFET ein- und der N-MOSFET ausgeschaltet,

- d. h., es fließt kein Strom durch die MOSFETs.

- Zwischen 4 V und 5 V ist der P-MOSFET aus- und der N-MOSFET eingeschaltet,

- d. h., es fließt kein Strom durch die MOSFETs.

- Zwischen 1 V und 3 V sind beide MOSFETs mehr oder weniger eingeschaltet,

- d. h., es kann ein Strom, ein Querstrom durch die MOSFETs fließen.

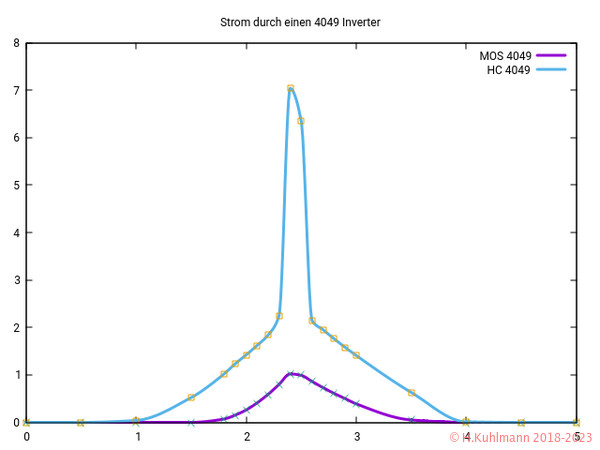

Messen wir den Strom durch den Inverter.

| Uein / V | CMOS Id / mA |

74HC Id / mA |

| 0.0 | 0.00 | 0.00 |

| 0.5 | 0.00 | 0.00 |

| 1.0 | 0.00 | 0.04 |

| 1.5 | 0.00 | 0.52 |

| 1.8 | 0.07 | 1.02 |

| 1.9 | 0.15 | 1.23 |

| 2.0 | 0.26 | 1.42 |

| 2.1 | 0.41 | 1.62 |

| 2.2 | 0.59 | 1.84 |

| 2.3 | 0.80 | 2.25 |

| 2.4 | 1.02 | 7.04 |

| 2.5 | 0.99 | 6.36 |

| 2.6 | 0.86 | 2.14 |

| 2.7 | 0.73 | 1.95 |

| 2.8 | 0.61 | 1.76 |

| 2.9 | 0.50 | 1.58 |

| 3.0 | 0.39 | 1.41 |

| 3.5 | 0.01 | 0.63 |

| 4.0 | 0.00 | 0.01 |

| 4.5 | 0.00 | 0.00 |

| 5.0 | 0.00 | 0.00 |

Tabelle 3

Diese Messungen bestätigen unsere Interpretation der Spannungsmessung.

Der Querstrom durch den 74HC4049 ist deutlich höher als im Standard-CMOS-4049. Offensichtlich sind die MOSFETs im 74HC4049 niederohmiger.

- Bei Eingangsspannungen nahe 0 V oder 5 V nehmen die 4049 sehr wenig Strom auf.

- Dagegen führt der Betrieb bei 2,5 V Eingangsspannung zu einem merklichen Querstrom durch das Gatter.

Umschaltstrom

Wenn sich der Zustand am Ausgang eines CMOS-Inverters oder -Gatters nicht ändert,

- fließt kein Querstrom durch das Gatter.

Ändert der Ausgang seinen Zustand 0→1 oder 1→0,

- fließt für eine sehr kurze Zeit (ns) ein Querstrom.

Je häufiger ein Zustandswechsel auftritt (hohe Frequenz),

- desto größer wird dieser Querstrom

- und der Strom durch das Gatter steigt.

- Interne Kondensatoren erzeugen weitere Umschaltströme.

Betriebsspannungen

CMOS-Bausteine können in einem weiten Bereich von Betriebsspannungen eingesetzt werden.

- Standard-CMOS zwischen 3 V und 15 V

- HC-CMOS zwischen 2 V und 6 V

Das Verhalten der CMOS-Inverter ist bei allen Betriebsspannungen Uv ähnlich.

- Liegt der Eingang bei 0 V oder Uv, fließt kein Querstrom im Gatter.

- Der Transfer liegt bei der halben Betriebsspannung, Uv/2.

- Im Bereich des Transfers kann ein Querstrom fließen.

CMOS-Gatter

In CMOS-Technologie können Gatter einfach aufgebaut werden.

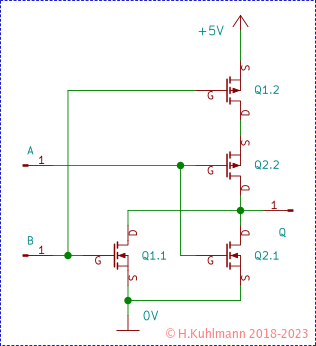

NOR

| A | B | Q |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Im Prinzip wird für jeden Eingang ein komplementäres Paar von MOSFETs verwendet.

- Die N-MOSFETs sind parallel und

- die P-MOSFETs in Reihe geschaltet.

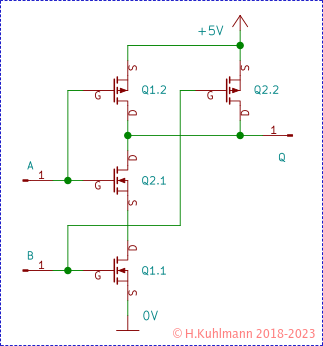

NAND

| A | B | Q |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Im Prinzip wird für jeden Eingang ein komplementäres Paar von MOSFETs verwendet.

- Die N-MOSFETs sind in Reihe und

- die P-MOSFETs parallel geschaltet.

Es ist wie beim Inverter:

- Solange die Eingangsspannung bei 0 V liegt, ist der P-MOSFET eines Paares ein- und der N-MOSFET ausgeschaltet.

- Solange die Eingangsspannung bei Uv liegt, ist der P-MOSFET eines Paares aus- und der N-MOSFET eingeschaltet.

- Wenn die Eingänge auf 0 V oder Uv liegen, fließt kein Querstrom durch die Gatter.

- Wenn alle Eingänge im Bereich der halben Betriebsspannung liegen, kann ein Querstrom durch das Gatter fließen.

Die meisten Logikbausteine in CMOS-Technologie sind nach diesem Prinzip aufgebaut.

Zusammenfassung

CMOS verwendet Paare von komplementären MOSFETs.

Die Gates eines Paares sind miteinander verbunden.

Wenn die Eingangsspannung eines Paares nahe 0 V liegt (logisch 0), ist der N-MOSFET aus- und der P-MOSFET eingeschaltet.

Wenn die Eingangsspannung eines Paares nahe der Betriebsspannung liegt (logisch 1), ist der N-MOSFET ein- und der P-MOSFET ausgeschaltet.

Für Gatter werden die MOSFETs der Paare in Reihe oder parallel geschaltet.

Die Paare sind immer so verschaltet, dass bei Eingangsspannungen von 0 V oder Betriebsspannung der Ausgang

- entweder 0 V ausgibt

- indem die N-MOSFETs auf 0 V schalten

- oder Betriebsspannung ausgibt,

- indem die P-MOSFETs auf Betriebsspannung schalten

- und kein Strom durch das CMOS-Gatter fließt.

Beim Umschalten des Gatterzustands fließt ein Umschaltstrom.

- Bei hohen Frequenzen steigt daher die Stromaufnahme von CMOS-Bausteinen.

Die Betriebsspannung liegt bei

- Standard-CMOS zwischen 3 V und 15 V

- HC-CMOS zwischen 2 V und 6 V.