Datenspeicher

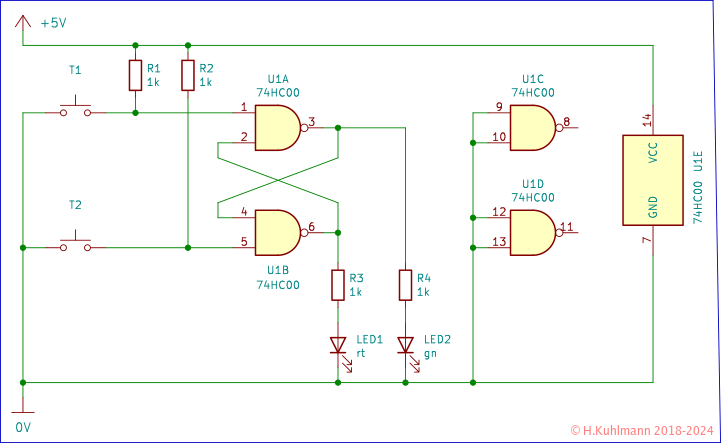

Datenspeicher mit RS-Flip-Flop

Fehlersuche

Beim Aufbau von Schaltungen treten immer wieder Fehler auf.

Dann hilft uns die Fehlersuche mit der LED-Anzeige.

Wir haben im Praktikum NAND-Gatter mit Gedächtnis gelernt, wie mit zwei NAND-Gattern ein einfacher Speicher, ein RS-Flip-Flop, aufgebaut wird.

-

Jeder Eingang wird über einen Widerstand auf 1 gelegt.

Bei Betätigung des Tasters wird eine 0 erzeugt.

Ein RS-Flip-Flop ist allerdings nicht einfach anzusteuern. Wir müssen vermeiden, dass beide Eingänge gleichzeitig 0 werden.

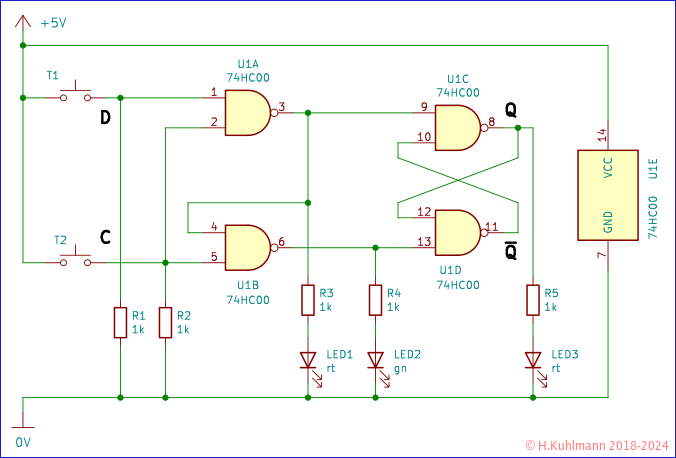

Die folgende Schaltung vermeidet diesen Nachteil.

Das D-Latch

-

Die Eingänge mit Taster und Widerstand in Bild 2 sind gegenüber Bild 1 umgekehrt.

Bei Betätigung eines Tasters wird eine 1 erzeugt.

Die Schaltung in Bild 2 ist ein einfacher Datenspeicher, meist D-Latch genannt. Er hat drei Anschlüsse:

- den Dateneingang D,

- den Takteingang C und

- den Datenausgang Q.

Eine Änderung des Zustands am Dateneingang (über Taster D) hat keine Wirkung auf die Ausgänge, wenn C=0 ist. Ist der Eingang C=1, folgt der Ausgang Q dem Dateneingang D. Q behält den Zustand bei, wenn C=0 ist.

Wer es nicht glaubt:

Die LED1 und LED2 zeigen, wie die Signale für das RS-Flip-Flop gebildet werden.

Diese Schaltung ist grundlegend und wir sollten sie auf dem Steckboard aufbauen und nachmessen.

Wir betrachten die Wahrheitstabelle eines D-Latches:

| D | C | Q | Q |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| x | 0 | Q | Q |

x meint 0 oder 1.

Der Ausgang Q ist NOT Q, also der invertierte Wert des Ausgangs Q.

Das D-Latch hat den Nachteil, dass der Ausgang Q dem Eingang D folgt, wenn C=1 ist. Wenn wir den Ausgang über eine Logik dem Eingang wieder zuführen würden, können wir Chaos erzeugen.

Auf der anderen Seite können gerade dadurch, dass die Zustände von Ausgängen über Logik auf Eingänge zurückgeführt werden, intelligente Schaltungen (Zustandsmaschinen) aufgebaut werden. Wir werden darauf noch eingehen. Moderne D-Speicher übernehmen deshalb den Zustand nicht, während der Takt aktiv ist, sondern mit einer Taktflanke.

- Eine Taktflanke ist der schnelle Übergang des Eingangs C

- von 0 nach 1 (positive Flanke),

- oder von 1 nach 0 (negative Flanke).

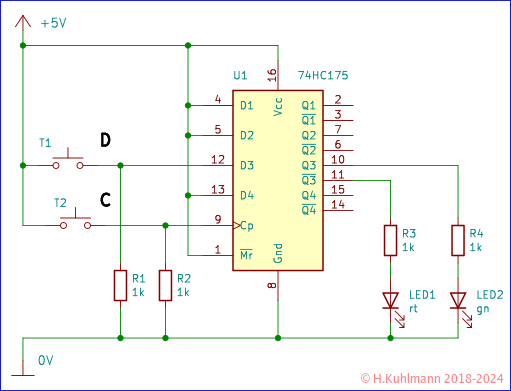

74HC175

Es gibt zwar den 74HC75 mit vier D-Latches. Wir nehmen jedoch aus den oben genannten Gründen einen 74HC175.

- Bei Betätigung eines Tasters wird eine 1 erzeugt.

Das D-Register 74HC175 hat alles, was zum Bau von Zustandsmaschinen benötigt wird.

- Der Zustand wird übernommen, wenn der Takt Cp von 0 nach 1 übergeht, mit der positiven Flanke ⭡ des Übergangs von 0 nach 1.

- Änderungen vor oder nach der Flanke haben keinen Einfluss auf den Wert im D-Register.

- Der 74HC175 hat den Eingang Mr, mit dem alle Q-Ausgänge auf 0 gesetzt werden.

- Wenn an Pin 1 eine 0 gelegt wird, werden alle D-Register zurückgesetzt.

- Wenn der 74HC175 eingeschaltet wird, hat er einen zufälligen Wert.

- Durch Mr wird der 74HC175 auf einen definierten Wert gesetzt.

- Der 74HC175 hat für jeden Ausgang Q einen invertierten Ausgang Q.

- Die Q sind hilfreich, wenn an das D-Register komplexe Logiken angeschlossen werden sollen.

- Der Eingang Mr (Master-Reset) wird manchmal auch mit Clr (Clear) bezeichnet.

Die Wahrheitstabelle für jedes D-Register ist:

| Mr | Cp | D | Q | Q |

| 0 | x | x | 0 | 1 |

| 1 | ⭡ | 1 | 1 | 0 |

| 1 | ⭡ | 0 | 0 | 1 |

| 1 | 0 | x | Q | Q |

| 1 | 0 | x | Q | Q |

Mit x ist ein beliebiger Wert (0 oder 1 oder Flanken) gemeint.

Mit dem ⭡ ist die Flanke von 0 nach 1 gemeint. Entsprechend ist ⭣ die Flanke von 1 nach 0.

Weitere Versuche

Der Zustand von Q3 sollte bei jedem Takt umschalten.

Wenn nicht, prellt der Taster für den Takt.

Welche Lösung gibt es gegen Prellen?

Regeln

- D-Latches und D-Register werden über einen Takt gesteuert.

- Zustandsgesteuerte D-Latches übernehmen das Datum am Eingang, wenn der Takt aktiv ist.

- Flankengesteuerte D-Register übernehmen das Datum am Eingang mit einer Taktflanke.

- Eine Flanke ist der Übergang:

- von 0 nach 1, positiv oder steigend ⭡,

- von 1 nach 0, negativ oder fallend ⭣.

- Mit einem Mr oder Reset-Eingang können D-Register auf einen definierten Wert (meist 0) gesetzt werden.

- Anstelle von Mr ist auch die Bezeichnung CRL gebräuchlich.

- Fast immer ist es besser, flankengesteuerte D-Register zu verwenden.